PA-RISC

PA-RISC je mikroprocesorová architektura vyvinutá společností Hewlett-Packard pro použití v serverech a integrovaných kancelářských systémech. Používá technologii RISC (Reduced Instruction Set Computing), PA v názvu označuje zkratku Precision Architecture („přesná architektura“). PA-RISC je také znám pod názvem HP/PA (Hewlett Packard Precision Architecture).

Koncem 80. let 20. století sestavila firma HP čtyři řady počítačů pracujících na různých CISC procesorech. Série HP VECTRA, vyráběná od roku 1986, byla osazena procesory Intel i286. Všechny ostatní modely využívaly CPU jiného výrobce. Mezi nimi byly modely HP Série 200 (1981) a HP 9000 Série 300 (1985) založené na procesoru Motorola 68000. (Po převzetí Apollo Computer v roce 1989 byla sestavena další série založená na M68000 označena HP Apollo 9000 Série 400 (1990)).

Nejbližší samostatná konstrukční řada byla série HP 300 (1978), integrovaný multiuživatelský počítač, který byl založen na Silicon on sapphire (SoS, „křemík na safíru“) a operačnímu systému Amigo/300. Také první konstrukční řada HP série 3000 (1972) se zakládala na SoS a operačním systému MPE. Konečná verze byl model HP 9000 Série 500 (1982), který byl použit u minipočítačů, který využíval (16- a 32bitový) FOCUS CPU vlastní výroby. Všechny HP systémy nepodporující procesory Intel byly díky novému PA-RISC-Procesoru v roce 1988 sjednoceny na stejný design.

První PA-RISC procesory byly 32bitové. Poprvé byly použity koncem 80. let v nových řadách HP 3000, konkrétně 930 a 950. Tyto stroje byly běžně známy pod názvem Spektrum, který dostaly ve vývojových laboratořích. Používaly operační systém MPE/iX. Počítače HP 9000 byly také upraveny na procesory PA-RISC a byl na nich použit HP-UX, verze operačního systému UNIX.

Mezi další operační systémy podporující procesory PA-RISC patří Linux, OpenBSD, NetBSD, NeXTSTEP a nevydaná verze Windows NT.

Zajímavou vlastností řady PA-RISC je, že většina jeho generací nemá žádnou cache druhé úrovně (L2). Místo toho je užívána velká cache první úrovně (L1). Dříve se jednalo o oddělené čipy připojené ke sběrnici, nyní bývá tato paměť integrována do procesoru. Pouze PA-7100LC a PA-7300LC měly vyrovnávací paměti druhé úrovně. Další inovace PA-RISC proběhla přidáním vektorových instrukcí (SIMD) ve formě MAX, které byly poprvé použity ve verzi PA-7100LC.

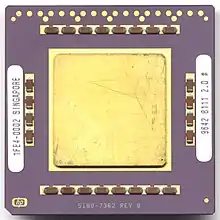

V roce 1996 došlo k dalšímu vylepšení návrhu, nová architektura PA-RISC 2.0 byla již plně 64bitová. Prvním produktem této řady byl PA-8000, který obsahoval deset funkčních jednotek a aktivní proudový systém zpracování dat (pipelining system). Další změnou bylo rozdělení cache pro instrukce na části podle toho, zda jednotlivé instrukce požadují dlouhé nebo krátké časy na dokončení úlohy.

Model PA-8500 obsahoval cache přímo v hlavním čipu, jednalo se o 1,5 MB cache L1 (1. úrovně), tím došlo k velkému nárůstu výkonu. S uvedením modelu došlo i k vylepšení Runway sběrnice o implementaci DDR, což umožnilo přistupovat do paměti rychlostí až 2GB/s. Jeho BHT (branch history table) se zdvojnásobila na velikost 2048 položek a TLB (translation lookaside buffer) se zvětšil ze 120 na 160 položek.

Model PA-8600 je přetaktovaná verze PA-8500 s mechanismem vyprazdňování kvazi-LRU instrukční cache (quasi-LRU instruction cache eviction policy). Model PA-8700 je taktován ještě rychleji než verze PA-8600, od které se liší pouze 2,25 MB L1 cache. Také byla vylepšen mechanismus vyprazdňování kvazi-LRU instrukční cache a mechanismus předčasného načítání dat (data prefetch capability). Za zmínku stojí, že poměrně vysoká latence integrované L1 cache (způsobená kompromisem vzhledem k její velikosti) může poněkud limitovat výkon. Nicméně velikost cache v procesorech HP zůstává ohromující.

Další verze PA-8800 (kódové označení Mako) obsahoval 2 nezávislé mikroprocesory na jediném čipu, jednalo se tak o dvoucestný SMP. Každý procesor v PA-8800 má 1,5 MB L1 cache, ale HP opouští svůj zvyk „pouze L1 cache“ a přidává také 32 MB L2 cache, která je oddělena. Runway sběrnice byl nahrazen 6,4 GB/s sběrnicí Zx1, poskytující větší šířku pásma a také použití velmi podobných serverových řešení pro PA-RISC a Itanium.

Model PA-8900 obsahuje 64 MB rychlejší L2 cache, která je sdílená a další drobná vylepšení jádra, jako je lepší detekci a oprava chyb cache. Jedná se o poslední model v řadě a nejedná se pouze o „posmrtnou křeč“ PA-8800, jak se dříve proslýchalo.

Návrh jádra představený s verzí PA-8000 se od té doby příliš nezměnil; každá další generace se soustředila především na zvýšení frekvence a na integraci dalších vylepšení (větší cache, dvě jádra…).

Modelová řada

| Model | Označení | Rok | Frekvence [MHz] | Paměťová sběrnice [MB/s] | Zpracování [µm] | Tranzistory [106] | Velikost [mm²] | Příkon [W] | datová cache [kB] | instrukční cache [kB] | L2 cache [MB] | ISA |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PCX-S | PA-7000 | 1989 | 66 | ? | 1.0 | 0.58 | 201.6 | ? | 256 | 256 | – | 1.1a |

| PCX-T | PA-7100 | 1992 | 33–100 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | – | 1.1b |

| PCX-T | PA-7150 | 1994 | 125 | ? | 0.8 | 0.85 | 196 | ? | 2048 | 1024 | – | 1.1b |

| PCX-T' | PA-7200 | 1994 | 120 | 960 | 0.55 | 1.26 | 210 | 30 | 1024 | 2048 | – | 1.1c |

| PCX-L | PA-7100LC | 1994 | 60–100 | ? | 0.75 | 0.9 | 201.6 | 7–11 | – | 1 | 2 | 1.1d |

| PCX-L2 | PA-7300LC | 1996 | 132–180 | ? | 0.5 | 9.2 | 260.1 | ? | 64 | 64 | 0–8 | 1.1e |

| PCX-U | PA-8000 | 1996 | 160–180 | 960 | 0.5 | 3.8/4.5? | 338/347? | ? | 1024 | 1024 | – | 2.0 |

| PCX-U+ | PA-8200 | 1997 | 200–240 | 960 | 0.5 | 3.8/4.5? | 338/347? | ? | 2048 | 2048 | – | 2.0 |

| PCX-W | PA-8500 | 1998? | 360–440 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | – | 2.0 |

| PCX-W+ | PA-8600 | 2000 | 552 | 1920 | 0.25 | 140 | 467 | ? | 1024 | 512 | – | 2.0 |

| PCX-W2 | PA-8700 | 2001 | 800–875 | 1920 | 0.18 | 186 | 304 | <7,1@1,5 V | 1536 | 768 | – | 2.0 |

| Mako | PA-8800 | 2003 | 800–1000 | 6400 | 0.13 | 300 | 361 | ? | 768/jádro | 768/jádro | 32 | 2.0 |

| Shortfin | PA-8900 | 2005 | 800–1100 | 6400 | 0.13 | ? | ? | ? | 768/jádro | 768/jádro | 64 | 2.0 |

Externí odkazy

- Hewlett Packard PA-RISC (PDF – anglicky)

- Komplexní informace o PA-RISC a počítačích (anglicky)

- Domácí stránka pro PA-RISC Linux (anglicky)

- HP zx1 chipset (anglicky)