MOSFET

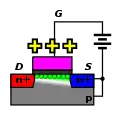

MOSFET je nejrozšířenější druh tranzistorů řízených elektrickým polem, u nichž je vodivost kanálu mezi elektrodami S a D řízena napětím mezi elektrodou G, která je tvořena kovem (nebo polykrystalickým křemíkem) odizolovaným od zbytku struktury tenkou vrstvičkou oxidu křemičitého.

Zkratka vyjadřuje:

- M (Metal) – řídicí elektroda je tvořena kovem (hliníkem)

- O (Oxide) – řídicí elektroda je izolována tenkou vrstvičkou oxidu křemičitého

- S (Semiconductor) – oxid je vytvořen na polovodičové destičce

- FET (Field effect transistor) – výsledkem je tranzistor řízený elektrickým polem

MOSFET (Metal Oxide Semiconductor Field Effect Transistor) je polem řízený tranzistor, u kterého je vodivost kanálu mezi elektrodami Source a Drain ovládána elektrickým polem vytvářeným ve struktuře kov(M)–oxid(O)–polovodič(S) napětím přiloženým mezi hradlo (Gate) a Source. Hradlo je odděleno od polovodiče vrstvou oxidu křemíku – odtud oxid v názvu tohoto typu tranzistoru.

Použití

Tranzistory MOSFET jsou základním aktivním prvkem většiny současné elektroniky, ve většině oblastí vytlačily klasické bipolární tranzistory. Používají se nejen v signálových digitálních a analogových obvodech, ale také ve výkonové elektronice, kde bylo jejich využití donedávna limitováno díky křemíkové technologii napětím zhruba 600V. V současnosti se již podařilo vyrobit tranzistory MOSFET i na bázi SiC (silikon-karbid) a GaAs (galium arsenid), což umožnilo rozšířit aplikační oblast do vyšších napětí a frekvencí.

Technologie výroby

Přestože unipolární tranzistory byly vynalezeny jako první z tranzistorů ve 20. letech 20. století, dlouho neexistoval postup jejich efektivní výroby. Tímto postupem se stala fotolitografie umožňující vytvářet na jedné destičce vyříznuté z monokrystalu křemíku postupně vrstvy oxidů, nitridů, které slouží jako masky, leptat obrazy struktur, ukládat hliník a polykrystalický křemík a pomocí dotování základního materiálu vytvářet různé druhy polovodičů a polovodičových přechodů.

Oxid křemičitý (SiO2), který lze poměrně snadno vytvářet na povrchu křemíku, tvoří izolaci mezi hradlem (gate), která poskytuje tomuto typu tranzistorů významné vlastnosti, a podle které byly i tranzistory nazvány. Elektroda hradla může být tvořena hliníkem. V technologii integrovaných obvodů je dnes velmi rozšířeno použití dotovaného polykrystalického křemíku, protože umožňuje výrobu tranzistorů s větší hustotou integrace a menšími parazitními kapacitami.

Postup výroby

Vytváření tranzistorových struktur na destičce polovodiče zahrnuje desítky kroků, které lze rozdělit do několika fází, v nichž se pomocí masky vytvořené fotografickým postupem vytvářejí jednotlivé části struktury tranzistoru nebo celého integrovaného obvodu:[1]

- V první fázi se vymezí aktivní oblasti jednotlivých tranzistorů

- Ve druhé fázi se vytvoří hradla tranzistorů ze silně dotovaného polykrystalického křemíku případně z hliníku

- Ve třetí fázi se pomocí difúze provede dotování oblastí elektrod S a D polovodičem opačné vodivosti, než má základní materiál a obnaží se místa pro kontakty jednotlivých elektrod

- Ve čtvrté fázi se čip pokryje vrstvičkou kovu (hliníku), v níž se leptáním vytvoří propojení jednotlivých prvků

Vymezení aktivní oblasti jednotlivých tranzistorů

V první fázi je základní destička polovodiče pokryta 1 μm silnou vrstvou oxidu křemičitého, která poslouží jako maska pro prostorové oddělení jednotlivých tranzistorů. Vytvoření aktivních oblastí pro tranzistory je realizováno odleptáním tohoto oxidu z příslušných oblastí. Pro tento účel je na oxid nanesena fotocitlivá vrstva, na níž jsou expozicí UV zářením vytvořeny oblasti, ze kterých bude oxid odleptán. Po odleptání je celá destička pokryta 0,1 μm tenkou vrstvou oxidu křemičitého sloužícího jako izolace hradel a potom je fotocitlivá vrstva odstraněna.

Při výrobě integrovaných obvodů CMOS se postupem podobným třetí fází vytváří N-vany pro tranzistory P-MOS. Pokud má obvod obsahovat tranzistory s vestavěným kanálem, následuje fáze v níž se iontovou implantací vytváří vodivé kanály pro tyto tranzistory.

Vytvoření elektrod G a spojů tvořených polykrystalickým křemíkem

Na destičce jsou vytvořena hradla nanesením hliníku nebo silně dotovaného polykrystalického křemíku.

Vytvoření oblastí elektrod S a D a spojů tvořených polykrystalickým křemíkem

Ve třetí fázi je pomocí pomocí difúze provedeno dotování materiálu základní destičky do hloubky asi 1 μm polovodičem opačné vodivosti, která určuje typ tranzistoru (P-MOS nebo N-MOS). Poté je destička opět pokryta tlustou vrstvou oxidu, v níž jsou opět fotolitograficky vytvořeny další masky sloužící pro vytvoření kontaktů jednotlivých elektrod.

Vytvoření kovových struktur propojujících jednotlivé tranzistory

V poslední fázi se čip pokryje vrstvičkou hliníku, ve kterém jsou odleptáním fotolitograficky vytvořeny spoje propojující jednotlivé tranzistory.

Rozdělení

- Dle typu polovodiče hradla (gatu)

CMOS – není druh tranzistoru, ale označení logických obvodů, které kombinují tranzistory NMOS a PMOS. Vždy je otevřený jen jeden z tranzistorů, druhým neprotéká téměř žádný proud. Toto řešení neexistuje v elektronkové verzi, jeho další výhodou je malý energetický úbytek.

- Dle typu vodivého kanálu (následující popis platí pro tranzistor N-MOS, u P-MOS je prohozena funkce děr a elektronů a popis platí pro opačné polarity napětí):

- s indukovaným kanálem: Mezi difundovanými příkopy tvořícími source a drain není vytvořen vodivý kanál a proto při UGS=0 neprochází mezi elektrodami drain a source žádný proud. Kanál vznikne vyloučením děr z procesu mezi drain a source a přitažených volných elektronů ze základní destičky při přiložení kladného napětí na hradlo G. Pod G převládne počet elektronů nad dírami a vznikne nová vrstva, která se chová podobně jako vodivý kanál s vodivostí typu N - toto platí pouze při kladném napětí hradla UGS>0.

- s vestavěným kanálem: Do povrchu slabě dotované základní destičky z křemíku, která má vodivost P, jsou difúzí vhodné příměsi vytvořeny 2 rovnoběžné příkopy se silnou koncentrací příměsí(N+), které tvoří drain (D, analogický k tranzistorovému kolektoru) a source (S, analogický k tranzistorovému emitoru). Mezi nimi je tenčí méně dotovaná vrstva N tvořící kanál. Nad ním je izolantem oddělené hradlo (G, gate). Přiložíme-li na hradlo záporné napětí proti source UGS<0, odpor kanálu se zvětší a při zvětšování UDS stoupá proud ID mírněji než při 0 předpětí hradla - tranzistor pracuje v režimu ochuzení (ochuzení kanálu o volné nosiče náboje).

Při závěrném předpětí UGSz vytlačí elektrické pole z kanálu všechny volné elektrony a proud ID klesne na nulu. Bude-li předpětí hradla proti source kladné, přitáhne naopak elektrické pole do prostoru kanálu volné elektrony (minoritní nosiče) ze základní destičky. Tím se zvětší vodivost kanálu a proud ID vzroste. Za této situace pracuje tranzistor v režimu obohacení.

Tento typ MOSFETů vyniká vyšším zesílením (větší strmost výstupní charakteristiky).

| typ kanálu | napětí gate-kanál | |||

|---|---|---|---|---|

| vodivý | n | vede | vede | nevede |

| indukovaný | n | vede | nevede | nevede |

| vodivý | p | nevede | vede | vede |

| indukovaný | p | nevede | nevede | vede |

Odkazy

Reference

- MOS fabrication process [online]. [cit. 2016-03-19]. Dostupné v archivu pořízeném dne 2016-09-10.

Související články

Externí odkazy

Obrázky, zvuky či videa k tématu MOSFET na Wikimedia Commons

Obrázky, zvuky či videa k tématu MOSFET na Wikimedia Commons