NMOS

NMOS logika (anglicky N-type metal-oxide-semiconductor) je technologie výroby logických integrovaných obvodů, které pro realizaci logických členů používají unipolární tranzistory s indukovaným kanálem (v obohaceném režimu) typu N.

Okolo roku 1975 získala NMOS logika dominantní postavení při výrobě složitých digitálních logických obvodů, především mikroprocesorů, které si (ve vylepšené verzi HMOS) udržela až do konce 80. let 20. století, kdy byla nahrazena logikou CMOS, která je sice výrobně složitější, ale umožňuje vytváření obvodů s vyšší integrací, nižší spotřebou a díky pokroku výroby a zmenšování rozměrů i větší rychlostí. V současnosti se již obvody NMOS téměř nepoužívají (s výjimkou specializovaných aplikací).

Zapojení hradel

Principiální zapojení hradla NAND tvořeného dvěma MOSFET s indukovaným kanálem N a se zátěží realizovanou rezistorem |

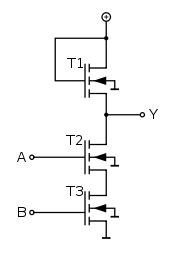

Hradlo NAND v NMOS se zatěžovacím tranzistorem T1 v obohaceném saturovaném režimu |

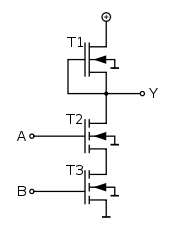

Hradlo NAND v NMOS se zatěžovacím tranzistorem T1 v obohaceném nesaturovaném režimu s UGG = Uth+UDD |

Hradlo NAND se zatěžovacím tranzistorem T1 se zabudovaným kanálem v ochuzeném režimu HMOS |

První písmeno „N“ zkratky NMOS vyjadřuje, že všechny unipolární tranzistory, z nichž se skládají logické obvody NMOS, jsou s kanálem typu N. Písmeno „M“ vyjadřuje, že řídicí elektroda G byla původně kovová (anglicky metal, později však převládlo používání polykrystalického křemíku), „O“ znamená, že je tato elektroda oddělenou od polovodivého substrátu tenkou vrstvou oxidu křemičitého (SiO2).

První z obrázků vpravo znázorňuje princip zapojení hradla NAND v technologii NMOS tvořeného dvěma MOSFET s indukovaným n-kanálem a zatěžovacím odporem: pokud je na oba vstupy A a B přivedeno kladné napětí, tranzistory T1 a T2 se otevřou a výstup Y stáhnou k zemi (nulovému napětí); ve všech ostatních případech bude alespoň jeden z tranzistorů zavřený a na výstupu Y bude díky rezistoru R kladné napětí. Chování obvodu lze shrnout následující tabulkou:

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Hradlo NOR lze realizovat podobně, výstupní elektrody D a S obou tranzistorů však nejsou zapojeny sériově, ale paralelně.

Realizace zatěžovacího odporu na čipu však zabírá extrémně velkou plochu (srovnatelnou s plochou desítek tranzistorů). V praktickém provedení NMOS obvodů byl proto místo zatěžovacího odporu použit další tranzistor FET s indukovaným n-kanálem, tj. stejného druhu jako jsou spínací tranzistory. Pro výrobu hradla NAND pak dostačují čtyři masky. Zatěžovací tranzistor působí v NMOS přibližně jako zdroj konstantního proudu, takže statická spotřeba je nižší než při použití zatěžovacího rezistoru s konstantní odporem. Při použití zatěžovacího tranzistoru v saturovaném režimu (druhý obrázek) má hradlo vyšší odběr a delší dobu přechodu do stavu logické nuly.

Třetí obrázek ukazuje zapojení hradla NAND se zatěžovacím tranzistorem T1 s indukovaným n-kanálem v obohaceném nesaturovaném režimu. Při zachování počtu výrobních kroků má toto řešení nejlepší vlastnosti, nevýhodou je nutnost dvou (případně tří) napájecích napětí.

Se zdokonalováním výrobních technologií bylo možné použít zatěžovací tranzistory s vodivým (vestavěným) kanálem, jak je znázorněno na čtvrtém obrázku. Výsledné obvody bývají označovány zkratkou HMOS (anglicky High density, short channel MOS). Jejich výhodou je potřeba pouze jednoho napájecího napětí a nižší ztráty, nevýhodou je o něco složitější výroba, protože pro vytvoření tranzistorů se zabudovaným kanálem (s vysokou impedancí) je zapotřebí alespoň pěti masek, tj. nejméně o jeden výrobní krok více, a poněkud větší plocha než pro spínací tranzistor.

Další unipolární technologie

PMOS

Logika PMOS, která využívá pouze tranzistory MOSFET s P-kanálem, byla díky jednodušší výrobě předchůdcem NMOS. Úlohu nosičů náboje plní u MOSFET s P-kanálem díry (chybějící elektrony), které mají nižší pohyblivost než elektrony, proto je logika PMOS pomalejší než NMOS.

HMOS

Při použití unipolárních tranzistorů s vodivým (vestavěným) kanálem v ochuzeném režimu lze vytvářet obvody, kterým stačí jediné napájecí napětí, dosahují vyšší rychlosti, menších rozměrů struktur a vyšší hustotu integrace, na úkor složitější výroby. Obvody nazývané různými výrobci HMOS, X-MOS, S-MOS, apod. navázaly na obvody NMOS.

CMOS

Pokrok v technologii výroby unipolárních číslicových integrovaných obvodů umožnil vytvářet obvody CMOS kombinující tranzistory s p-kanálem a n-kanálem, které mají mnohem menší statickou spotřebu než obvody NMOS. Původní CMOS obvody byly velmi pomalé, zmenšování struktur však přineslo jejich významné zrychlení.

Odkazy

Reference

V tomto článku byl použit překlad textu z článku NMOS-Logik na německé Wikipedii.

Literatura

- Jerry C. Whitaker. Microelectronics. 2. vyd. [s.l.]: CRC Press, 2005. ISBN 0849333911.

- M. Glesner et. al. Vorlesungsskriptum - VLSI Design of Integrated Circuits. [s.l.]: Darmstadt University of Technology

- Christian Clemen. NMOS-Inverter. [s.l.]: Fachhochschule Augsburg, 2000. Dostupné online.

Externí odkazy

Obrázky, zvuky či videa k tématu NMOS na Wikimedia Commons

Obrázky, zvuky či videa k tématu NMOS na Wikimedia Commons