RISC-V

RISC-V (výslovnost [ˌrisk ˈfaiv]; V je římská číslice 5) je otevřená instrukční sada z rodiny RISC. Je vyvíjena od roku 2010 na Kalifornské univerzitě v Berkeley. Původně šlo o “tříměsíční projekt”, který měl vytvořit novou otevřenou instrukční sadu (architekturu) na základě existujících technologií a překonat tak omezení související s proprietárními architekturami, mezi něž patří:

- Patentová ochrana – vyšší náklady

- Provázanost mezi vlastnictvím architektury a návrhem procesorů – nemožnost změny dodavatele

- Složitost mnoha architektur – často zbytečná

- Architektura může zaniknout zároveň se společností, která ji vlastní – riziko v čase

Na rozdíl od starších projektů majících rovněž za cíl vytvářet procesory jako otevřený hardware (např. DLX a OpenRISC) je RISC-V navržen pro široké použití od vestavěných systémů přes mobilní telefony až po cloudové počítače, tedy s důrazem na výkon i na spotřebu.

Instrukční sada RISC-V je od počátku otevřená, nicméně velký komerční zájem vedl v roce 2015 k založení oficiální neziskové organizace RISC-V Foundation, jejímž cílem bylo podpořit počáteční přijetí RISC-V a dále tuto instrukční sadu udržovat a rozvíjet. Původní autoři a vlastníci se vzdali svých práv ve prospěch organizace. RISC-V Foundation měla 36 zakládajících členů a svými členy je nadále řízena. V roce 2020 došlo k transformaci na mezinárodní sdružení RISC-V International, které sídlí ve Švýcarsku a je zodpovědné za další vývoj architektury RISC-V[1].

Softwarová podpora

Z operačních systémů ohlásilo podporu jako první FreeBSD. To podporuje RISC-V od verze 11.0 z října 2016.[2] Začátkem dubna 2018 byl po zhruba roce příprav oficiálně založen port operačního systému-linuxové distribuce Debian na 64bitovou variantu RISC-V.[3] Mezi další operační systémy, které podporují RISC-V, patří FreeRTOS[4] a ThreadX.

Vlastnosti

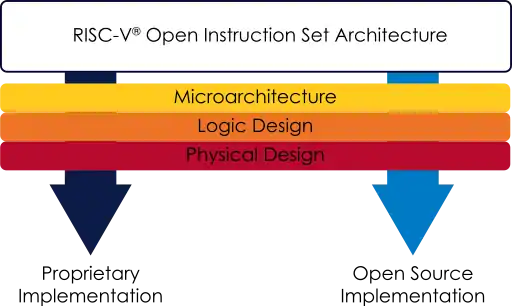

Instrukční sada RISC-V má několik specifik. Předně nestanovuje žádnou konkrétní mikroarchitekturu ani licenční model, je vysoce modulární a díky podpoře RISC-V International nezávislá na konkrétním dodavateli.

Na rozdíl od podobných projektů, které se zaměřují na otevřený hardware, RISC-V stanoví pouze instrukční sadu (ISA); mikroarchitektura záleží na konkrétní implementaci a nemá žádná omezení daná standardem RISC-V.

Vývojáři procesorových jader založených na RISC-V si navíc mohou zvolit libovolný licenční model. Někteří používají komerční licence, jiní otevřené (viz dále).

Nejdůležitější vlastností instrukční sady RISC-V je však její univerzálnost. Tvůrci měli na paměti, že různé aplikace vyžadují různou složitost architektury, proto vytvořili vysoce modulární standard: Základní instrukční sada RISC-V je velmi minimalistická (pouze 49 instrukcí pro 32bitový procesor) a nabízí množství volitelných standardních rozšíření. Navíc je k dispozici dobře definovaná možnost vytvořit si vlastní, nestandardní instrukce podle potřeby.

Ukazuje se, že přidání vhodných vlastních instrukcí představuje velmi výhodnou cestu ke zvýšení výkonu procesoru[5][6].

Implementace

Komerčně licencovaná jádra RISC-V

- Andes Technology Corporation nabízí několik různých sérií jader s volitelným rozšířením instrukční sady, včetně možností pro návrh vícejádrových systémů[7]:

- Série N(X) zahrnuje jak 32bitová jádra (N), tak i 64bitová (NX). Délka pipeline (zřetězené linky) je různá, od dvoustupňové u jádra N22 až po osmistupňovou u N45. Jádro NX27V podporuje vektorové rozšíření RISC-V neboli sadu “V”[8].

- Série D(X) nabízí jádra s instrukční sadou “P”, která podporuje operace SIMD, a na výběr jsou opět jádra 32bitová (D) i 64bitová (DX).

- Série A(X) se zaměřuje na aplikační procesorová jádra s podporou Linuxu a délkou pipeline od pěti do osmi stupňů. Dále nabízí podporu operací s plovoucí desetinnou čárkou a jednotku pro správu paměti (MMU).

- Původem česká společnost Codasip s.r.o. (dnes součást skupiny Codasip GmbH) v lednu 2016 uvedla na trh historicky první komerční jádro založené na RISC-V (Codix)[9] a dnes má v nabídce několik sérií vestavěných i aplikačních procesorových jader RISC-V. Jádra od Codasipu jsou navržena v proprietárním jazyce CodAL[10] a firma je vyvíjí s pomocí patentované technologie a vlastního návrhového nástroje zvaného Codasip Studio.

- Série L nabízí minimalistická 32bitová jádra s nízkou spotřebou, pipeline o délce tří nebo pěti stupňů a volitelným rozšířením pro operace s plovoucí desetinnou čárkou.

- Série H nabízí 64bitová vestavěná jádra s vysokým výkonem. Volitelně je opět k dispozici rozšiřující sada pro operace s desetinnou čárkou.

- Série A obsahuje 64bitová jádra, která podporují Linux a lze je rozšířit o instrukční sadu “P”. Jádra mají sedmistupňovou pipeline, podporu operací s desetinnou čárkou (FPU) a správu paměti (MMU). Verze jader rodiny A s příponou -MP navíc obsahují cache (vyrovnávací paměti) L1 a L2 a nabízejí podporu pro vícejádrový systém o maximálním počtu čtyř jader[11].

- Jádro uRISC-V, které je součástí nástroje Codasip Studio, slouží ke vzdělávacím a výukovým účelům[12].

- Společnost SiFive začala prodávat v květnu 2017 jednodeskový počítač kompatibilní s Arduinem a postavený na RISC-V procesoru Freedom E310. Táž společnost oznámila v říjnu 2017 dokončení návrhu čtyřjádrového 64bitového procesoru U54-MC Coreplex, který je navržen pro taktovací kmitočet 1,5 GHz a na kterém bude možné spustit plnohodnotný desktopový operační systém, například Linux.[13][14] V únoru 2018 tato společnost spustila prodej jednodeskového počítače HI-Five Unleashed.[15] Společnost SiFive momentálně nabízí tři hlavní řady produktů:

- Série E zahrnuje 32bitová vestavěná jádra s dvou- až osmistupňovou pipeline. Nejpokročilejší z této série je čtyřjádrový procesor E76-MC.

- Série S zahrnuje 64bitová vestavěná jádra s dvou- až osmistupňovou pipeline. Nejpokročilejší z této série je S76-MC.

- Série U představuje nabídku 64bitových aplikačních jader o délce pipeline 5–12 stupňů. Varianty U54 a U74 jsou k dispozici ve vícejádrové verzi. Superskalární jádro U84 nabízí nejvyšší výkon z této série[16].

- Intelligence X280 je aplikační jádro odvozené ze série U, které navíc podporuje vektorové rozšíření „V“[17].

Otevřená jádra RISC-V

- Kalifornská univerzita v Berkeley vyvinula řadu procesorových jader RISC-V s využitím jazyka Chisel:

- 64bitové jádro Rocket[18] vhodné pro kompaktní zařízení s nízkou spotřebou, jako je přenosná osobní elektronika.

- 64bitové superskalární jádro Berkeley Out of Order Machine (BOOM)[19] s instrukční sadou RV64GC, určené jak pro osobní počítače, tak i pro superpočítače a databázové servery.

- Pět návrhů 32bitového procesoru Sodor[20], které slouží primárně pro studentské projekty.

- PULPino (Riscy a Zero-Riscy), projekt Spolkové vysoké technické školy v Curychu / Boloňské univerzity[21]. Jádra PULPino implementují jednoduchou instrukční sadu RV32IMC pro mikrokontroléry (Zero-Riscy) nebo výkonnější sadu RV32IMFC s rozšířením pro zpracování digitálního signálu (DSP).

- Společnost Western Digital vyvinula několik vlastních RISC-V jader pod názvem SweRV Cores a poskytla je volně pod otevřenou licencí prostřednictvím CHIPS Alliance. Komerční podporu těchto jader poskytuje ve spolupráci s Codasipem[22]. Jádra SweRV cílí na výkonné vestavěné systémy a implementují základní sadu RV32IMC:

- SweRV Core EH1 je dvouvláknové superskalární jádro s devítistupňovou pipeline.

- SweRV Core EH2[23] je superskalární jádro se dvěma hardwarovými vlákny a devítistupňovou pipeline.

- SweRV Core EL2 je minimalistické jednovláknové jádro se čtyřstupňovou pipeline.

Reakce konkurence

Holding ARM, významný designér procesorů a software, spustil v červenci 2018 PR kampaň mířící proti architektuře RISC-V; ta se snaží v pěti bodech potenciálním zákazníkům vysvětlit, jak riskantní volbou je pro ně RISC-V oproti ARMu.[24]

Odkazy

Reference

- RISC-V International [online]. [cit. 2021-06-01]. Dostupné online. (anglicky)

- FIKAR, Jan. Vydáno FreeBSD 11.0 s podporou RISC-V. Unixy. root.cz [online]. Internet Info, s.r.o., 11. říjen 2016 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309. (česky)

- KRČMÁŘ, Petr. Debian přidává podporu pro 64bitovou architekturu RISC-V. Linux. root.cz [online]. Internet Info, s.r.o., 5. duben 2018 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309. (česky)

- FreeRTOS for RISC-V RV32 and RV64. FreeRTOS [online]. [cit. 2021-07-28]. Dostupné online. (anglicky)

- Download Codasip Whitepaper on RISC-V Processor Customization. us17.campaign-archive.com [online]. [cit. 2021-07-30]. Dostupné online.

- BELHADJ AMOR, Hela; BERNIER, Carolynn; PRIKRYL, Zdenek. A RISC-V ISA Extension for Ultra-Low Power IoT Wireless Signal Processing. IEEE Transactions on Computers. 2021, s. 1–1. Dostupné online [cit. 2021-07-30]. ISSN 1557-9956. DOI 10.1109/TC.2021.3063027.

- CORPORATION, Andes Technology. Andes Announces New RISC-V Processors: Superscalar 45-Series with Multi-core Support and 27-Series with Level-2 Cache Controller. GlobeNewswire News Room [online]. 2020-11-30 [cit. 2021-06-01]. Dostupné online. (anglicky)

- DAHAD, Nitin. EETimes [online]. 2019-12-10 [cit. 2021-06-01]. Dostupné online.

- Codasip Joins RISC-V Foundation and Announces Availability of RISC-V Compliant Codix Processor IP. Design And Reuse [online]. [cit. 2021-06-01]. Dostupné online. (anglicky)

- What is CodAL?. Codasip [online]. 2021-02-26 [cit. 2021-06-17]. Dostupné online. (anglicky)

- Codasip announces RISC-V processor cores providing multi-core and SIMD capabilities. www.newelectronics.co.uk [online]. [cit. 2021-06-01]. Dostupné online.

- Codasip Releases a Major Upgrade of Its Studio Processor Design Toolset with a Tutorial RISC-V core. Design And Reuse [online]. [cit. 2021-06-01]. Dostupné online. (anglicky)

- FIKAR, Jan. SiFive začalo licencovat první RISC-V procesor, na kterém poběží Linux. Kompilery a procesory. root.cz [online]. Internet Info, s.r.o., 9. říjen 2017 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309. (česky)

- OLŠAN, Jan. První plnohodnotný procesor RISC-V podporující Linux je tu, budou i vývojářské desky. Hardware. cnews.cz [online]. Mladá fronta a. s., 14. říjen 2017 [cit. 2018-07-12]. Dostupné online. (česky)

- KRČMÁŘ, Petr. Hi-Five Unleashed: první linuxový počítač s procesorem RISC-V. PC a notebooky. root.cz [online]. Internet Info, s.r.o., 9. únor 2018. Dostupné online. ISSN 1212-8309. (česky)

- SiFive Announces U8-Series 2.6GHz High-Performance Out-of-Order RISC-V Core IP. Hackster.io [online]. [cit. 2021-06-01]. Dostupné online. (anglicky)

- SCHILLING, Andreas. Neuer Intelligence X280 von SiFive verbindet RISC-V mit Vektorbeschleunigung. Hardwareluxx [online]. [cit. 2021-06-01]. Dostupné online. (německy)

- chipsalliance/rocket-chip. github.com [online]. 2021-05-31 [cit. 2021-06-01]. Original-date: 2014-09-12T07:04:30Z. Dostupné online.

- riscv-boom/riscv-boom. github.com [online]. 2021-05-29 [cit. 2021-06-01]. Original-date: 2014-01-21T17:18:10Z. Dostupné online.

- ucb-bar/riscv-sodor. github.com [online]. 2021-05-25 [cit. 2021-06-01]. Original-date: 2013-07-17T22:10:42Z. Dostupné online.

- PULP platform. www.pulp-platform.org [online]. [cit. 2021-06-01]. Dostupné online.

- Codasip partners with Western Digital on open‑source processors. eeNews Europe [online]. 2019-12-10 [cit. 2021-06-01]. Dostupné online. (anglicky)

- SHILOV, Anton. Western Digital Rolls-Out Two New SweRV RISC-V Cores For Microcontrollers. www.anandtech.com [online]. [cit. 2021-06-01]. Dostupné online.

- ARM v kampani útočí na RISC-V. Periferie. root.cz [online]. Internet Info, s.r.o., 10. červenec 2018 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309. (česky)

Externí odkazy

- (anglicky) Oficiální stránka projektu

- (česky) TIŠNOVSKÝ, Pavel. Instrukční sada procesorových jader s otevřenou architekturou RISC-V. root.cz [online]. Internet Info, s.r.o., 5. listopad 2015 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309.

- (česky) TIŠNOVSKÝ, Pavel. Otevřené RISCové architektury OpenRISC a RISC-V. root.cz [online]. Internet Info, s.r.o., 29. říjen 2015 [cit. 2018-07-12]. Dostupné online. ISSN 1212-8309.