Logická úroveň

Logická úroveň je reprezentace logické hodnoty v číslicové technice určitým stavem elektrického obvodu, nejčastěji úrovní elektrického napětí vůči společnému vodiči. Mimo elektroniku mohou pro reprezentaci logické úrovně sloužit i jiné fyzikální veličiny (tlak v pneumatických systémech, intenzita světla v optoelektronice).

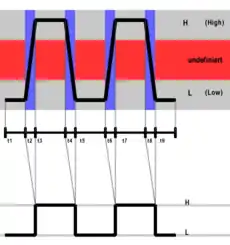

V naprosté většině případů rozlišujeme dvě úrovně, Vysokou úroveň (H-level a High, H) a Nízkou úroveň (L-level, Low, L).

Napěťové úrovně

V digitální technice je nositelem informace obvykle elektrické napětí. Protože informace bývají kódované zpravidla binárně, používají se dvě napěťové úrovně, případně intervaly. Vysoká úroveň je napětí blízké napájecímu VDD. Nízká úroveň se obvykle blíží 0 voltům (referenční zem, zkrat na zem - anglicky GND). Přesné hodnoty napětí se liší v podle typu použitých obvodů (podle "rodiny" digitální logiky). Nízká napěťová úroveň obvykle reprezentuje logickou nulu, vysoká úroveň logickou jedničku.

Obvykle se používají stejnosměrná napětí v řádu několika voltů (5V, 3,3V, 2,5V, 1,8V, 1,2V). V silnoproudých obvodech se setkáváme i s reléovou logikou pracující s napětím 24V DC, případně 230V AC.

Běžné logické obvody obvykle připouštějí na svých vstupech pro tyto dvě napěťové úrovně poměrně vysoké tolerance. Hodnota VIL definuje maximální napětí reprezentující nízkou úroveň. Hodnota VIH definuje minimální napětí reprezentující vysokou úroveň. Mezi VIL a VIH leží zakázané pásmo, ve kterém není logická hodnota jednoznačně určena (na obrázku červeně). Na výstupech logického obvodu je zaručeno pro vysokou úroveň napětí minimálně VOH, na vstupech je pro vysokou úroveň požadováno napětí minimálně VIH. Výstupní napětí VOH je vždy větší než vstupní napětí VIH, rozdíl VOH − VIH zajišťuje provozní odolnost obvodů proti rušení. Podobně u nízké úrovně je maximální výstupní napětí VOL, maximální vstupní napětí VIL, odolnost proti rušení je daná rozpětím VIL − VOL.

K vyčerpání rezervy tolerancí napěťových úrovní a tedy k přechodu do zakázané oblasti může vést několik faktorů. Například výstupní napětí hradla závisí na proudu zátěže a počtu připojených vstupů. Rovněž se mohou uplatnit indukční a kapacitní vazby, nebo vnější zdroje rušení. Dále nevhodná kombinace součástek použitých při výrobě (různé logické rodiny), nebo posun parametrů vedení a optických komponent vlivem teploty.

Přechod mezi dvěma logickými úrovněmi musí proběhnout rychle, protože prochází zakázaným pásmem. Označujeme jej jako "hranu signálu" (v grafu znázorněno modře). Pokud spínací hrany nejsou dostatečně ostré, nebo pro potřebu převodu analogového signálu na digitální signál může být použit Schmittův obvod.

Standardní logické úrovně

| Vstupní úroveň |

Výstupní úroveň | |||

|---|---|---|---|---|

| Technologie | Nízká (VIL) | Vysoká (VIH) | Nízká (VOL) | Vysoká (VOH) |

| TTL 5V | ≤ 0,8 | ≥ 2,0 | ≤ 0,4 | ≥ 2,4 |

| CMOS 5V | ≤ 1,5 | ≥ 3,5 | ≤ 0,5 | ≥ 4,44 |

| LVTTL 3.3V | ≤ 0,8 | ≥ 2,0 | ≤ 0,4 | ≥ 2,4 |

| CMOS 2.5 V | ≤ 0,7 | ≥ 1,7 | ≤ 0,2 | ≥ 2,3 |

| CMOS 1,8 V | ≤ 0,7 | ≥ 1,17 | ≤ 0,45 | ≥ 1,2 |

| CMOS obecně | ≤ 1/3 VDD | ≥ 2/3 VDD | ? | ? |

| ECL | ≤ -1,4 | ≥ -1,2 | ? | ? |

| RS-232(*) | -15 až -3 | +3 až +15 | -15 až -5[1] | +5 až +15[1] |

| HTL 10...30V | ≤ 0,2 × VDD | ≥ 0,6 × VDD | ≈ VDD | |

| (*) = negativní logika, d. h. nízká=1, střední=0 | ||||

Typy logiky

Signály aktivní v nule a v jedničce

Binární signály, které nereprezentují číslicové údaje, ale indikují určitý stav, mohou být "aktivní v nule", nebo "aktivní v jedničce". To znamená, že stav nebo podmínka naznačená jménem signálu je splněna buď při logické úrovni nula nebo jedna.

Signály aktivní v nule se obvykle značí vodorovnou čárou nad jménem. Alternativně se používají třeba hvězdičky nebo lomítka před nebo za jménem signálu. Označení BSP, *BSP nebo /BSP naznačuje, že signál BSP je aktivní v nule.

Tato identifikace signálů jako aktivních v nule nebo v jedničce je závislá na pojmenování. Například označení řídicího vstupu /ena (enable = povolit, aktivní v nule) může být rovnocenné označení dis (disable = zakázat, aktivní v jedničce).

Pozitivní a negativní logika

V tzv. pozitivní logice kóduje na vysoká, úroveň binární hodnotu 1 a nízká úroveň binární hodnotu 0. V negativní logice reprezentuje vysoká úroveň logickou nulu a nízká -úroveň logickou jedničku.

Pro lepší odolnost proti rušení se pro řídicí signály často používá negativní logika – například u rozhraní RS-232. Také u rozhraní IEC-625 je celý handshaking implementovaný v negativní logice.

Pozitivní a negativní logika je však v digitální technologii pouhou otázkou notace. Pokud je signál místo v pozitivní logice, v negativní logice (nebo naopak), odpovídá to negaci na všech dotčených vstupech a výstupech. Například, mějme hradlo se vstupy A, B a výstupem Y.

Pokud změníme signály na vstupech A, B z pozitivní logiky na negativní, musíme změnit logickou funkci podle De Morganova pravidla.

Z hradel AND pro pozitivní logiku se staly hradla OR pro negativní logiku.

Převod logických úrovní

Někdy je nutné používat obvody s různou úrovní napájení VDD. Z hlediska VIH a VIL jsou kompatibilní např. obvody TTL 5V a LVTTL 3V. Aby však bylo možno zapojit "5V TTL" výstup do "3,3V LVTTL" vstupu, je nutné aby LVTTL obvod byl "5V tolerantní". Pro spojování různých typů digitální logiky existují také speciální obvody.

Třístavová logika

Ve třístavové logice může být výstup kromě stavů logická 0 a logická 1 také ve stavu vysoké impedance (Z), při kterém neovlivňuje vstupy připojených logických obvodů.

Čtyřstavová logika

Jedná se o rozšíření určené pro návrh logických obvodů. Ke stavům 0,1 a Z se přidává stav X, který znamená, že na logické hodnotě nezáleží.

Devítistavová logika

Jedná se o abstrakci logiky pro návrh a simulaci logických obvodů. Na devítistavové logice je postaven například návrhový jazyk VHDL.

Literatura

- JEDEC/EIA: JESD8-C.01: Interface Standard for Nominal 3 V/3.3 V Supply Digital Integrated Circuits. EIA, r.v. 2007. (Anglicky, standard LVTTL 3,3 V)

- JEDEC/EIA: JESD8-5A.01: 2.5V ± 0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuit. EIA, r.v. 2007. (Anglicky standard pro CMOS 2,5 V)

- JEDEC/EIA: JESD8-7A: 1.8V ± 0.15V (Normal Range), and 1.2V - 1.95V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuit. EIA, ó.O. 2006. (Anglicky, standard pro CMOS 1,8 V)

Reference

V tomto článku byly použity překlady textů z článků Logikpegel na německé Wikipedii a Logic level na anglické Wikipedii.