Bistabilní klopný obvod

Bistabilní klopný obvod (BKO, flip-flop, latch, případně bistabilní multivibrátor) je klopný obvod, který má dva stabilní stavy. Mezi těmito stavy lze přepínat pomocí signálů přivedených na vstupy. Tyto obvody se proto používají jako paměťové prvky.

BKO mají mnoho variant a provedení. Nejznámější jsou: RS, JK, D a T.

Druhy bistabilních klopných obvodů

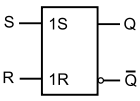

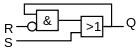

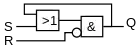

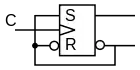

Klopný obvod RS

RS je jedním z nejzákladnějších a nejjednodušších BKO.

Vstup R se označuje jako Reset. Přivedení hodnoty logická 1 na tento vstup vynuluje hodnotu Q (neboli nastaví výstup na hodnotu logická nula).

Vstup S se označuje jako Set, přivedení hodnoty logická 1 na tento vstup nastaví hodnotu Q na logickou 1.

Pokud je na R a S zároveň logická 1, mluvíme o zakázaném nebo také hazardním stavu. Znamená to, že tento stav není definován a pokud nastane tato vstupní kombinace, není předem možné určit, v jakém stavu se bude nacházet výstup obvodu.

Aby se tomuto stavu zabránilo, konstruují se tzv. RS obvody s prioritou. A to buď set nebo reset. V případě, že by u normálního obvodu mělo dojít k hazardnímu stavu, obvod s prioritou se přepne buď do 1 (priorita set) nebo do 0 (priorita reset).

Pojem zakázaný stav pochází z doby, kdy byl tento obvod realizován dvěma invertory, u kterých nebyl eliminován zpětný přenos přes jednotlivé tranzistory. Současné buzení obou vstupů vedlo k tomu, že se výstupní veličiny dostávaly do zakázaného pásma a tranzistory přecházely ze saturace do aktivní zóny svých charakteristik.

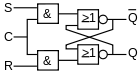

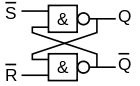

RS klopný obvod lze realizovat pomocí dvou dvouvstupých hradel typu NAND nebo NOR.[1] Výstup prvního členu se vede do jednoho ze vstupů druhého členu, výstup druhého se vede do jednoho ze vstupů prvního. Druhé vstupy členů slouží jako vstupy R a S. V případě RSKO sestaveného z členů NAND jsou tyto vstupy aktivní v logické nule.

|

|

Vysvětlivky: • Qn aktuální stav (čas t+0) • Qn+1 stav následující (čas t+1) • X hazardní stav ve kterém neplatí negace mezi Q a Q, RSKO sestavený z NAND zaujme , RSKO sestavený z NOR potom | |||||||||||||||||||||||||||||||||||||

Tento typ obvodu se často využívá pro ošetření signálu z mechanických přepínačů, u nichž obvykle dochází k zákmitům kontaktů a tím i k nežádoucímu vyslání několika impulsů. Připojením přepínače na vstupy RS obvodu lze vzniku nežádoucích impulsů zabránit. Nevýhodou tohoto způsobu je, že vyžaduje přepínací kontakt, výhodou je naprosto spolehlivé potlačení zákmitů na rozdíl od použití dolnopropustných filtrů nebo monostabilních obvodů. Hlavní použití RSKO je pro jednoduché paměťové funkce (zapnuto-vypnuto) nebo jako součást složitějších struktur popsaných dále.

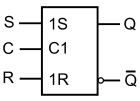

Doplněním dalších dvou členů AND zapojených jako blokování vstupů lze realizovat synchronní variantu tohoto klopného obvodu. Obvod tak bude reagovat na vstupy pouze po dobu a nebo pouze v době, kdy je hodinový signál C ve stavu log.1. Pokud je vstup signálu C vybaven detekcí náběžné hrany, bude se stav výstupů měnit pouze v okamžiku náběžné hrany signálu.

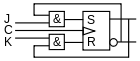

Klopný obvod JK

JK má vstupy funkčně shodné s obvodem RS: J nastavuje hodnotu logická 1, vstup K nastavuje hodnotu logická 0. Pokud jsou oba vstupy J a K aktivní (u KO RS mluvíme o zakázaném stavu), vnitřní hodnota se při hodinovém pulzu neguje. Oproti RS se tento klopný obvod vyrábí pouze v synchronní variantě.

Tento obvod nese označení po vědci jménem Jack Kilby (proto zkratka JK), který jej v roce 1958 představil ve firmě Texas Instruments (patent na jeho jméno vyšel o rok později). Protože název obvodu nemá žádný odvozený význam, existuje v angličtině mnemotechnická pomůcka pro označení vstupů „jump-kill“, tedy „nahoď-zruš“.

|

Vysvětlivky: • Qn aktuální stav (čas t+0) • Qn+1 stav následující (čas t+1) • X nedefinovaný stav (log.0 nebo log.1) je u tohoto klopného obvodu ošetřen | |||||||||||||||||||

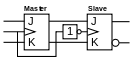

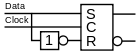

Klopný obvod JK Master-Slave

JK Master-Slave je klopný obvod tvořený dvěma klopnými obvody JK. První master (nadřízený člen), druhý slave (podřízený člen). Princip činnosti je v tom, že klopný obvod má kaskádně zapojeny vstupy J, K. Vstup Clk (není značen) řídí stav jednotlivých obvodů následovně: master reaguje na vzestupnou hranu, Slave na sestupnou hranu společného signálu Clk. Master má vstupy J, K a Clk, výstupy jsou přivedeny na vstupy Slave, jehož výstupy teprve vedou na výstup celého klopného obvodu. Při vzestupné hraně signálu Clk master načte data (stav J, K), ale na výstupu slave se objeví až při sestupné hraně signálu Clk.

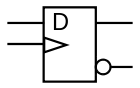

Klopný obvod D

Obvod D realizuje jednobitovou paměť. Z obvodu RS se snadno vyrobí tím, že na vstup R přivedeme negovanou hodnotu vstupu S. Výstupy klopného obvodu kopírují stav vstupního signálu Data po dobu, po kterou je vstupní signál Clk ve stavu log.1. Při hodnotě log.0 na vstupu Clk zůstává na výstupech zachován poslední stav, který byl zapamatován při hodnotě Clk = log.1. Český název zdrž, anglicky delay.

Pokud je vstup Clk vybaven detekcí náběžné hrany, zapamatuje se stav vstupu Data v okamžiku náběžné hrany.

|

Vysvětlivky: • Qn+1 stav následující (čas t+1) • X nedefinovaný stav (log.0 nebo log.1) u tohoto klopného obvodu nenastává | |||||||||

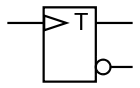

Klopný obvod T

Obvod T je přepínač paměti. S každou náběžnou hranou dojde ke změně výstupního stavu na inverzní k předchozí. V principu se jedná o děličku frekvence hodnotou 2 (fout = fin / 2).

U druhé varianty dochází ke změně na výstupech pouze tehdy, je-li řídící vstup ve stavu log.1.

Synchronní variantu je možné realizovat pomocí klopného obvodu JK spojením jeho vstupů J a K. Asynchronní variantu je možno realizovat ze synchronní připojením signálu hodin ke vstupnímu signálu.

Odkazy

Reference

- MALINA, Václav. Digitální technika. České Budějovice: KOPP, 2001. ISBN 80-85828-70-7. Kapitola 2.2, s. 49–59. (česky)

Literatura

- HÁJEK, J.: 2× ČASOVAČ 555: praktická zapojení, nakladatelství BEN - technická literatura, ISBN 80-86056-27-9.

- MALINA, V.: Digitální technika, nakladatelství KOPP, ISBN 80-85828-70-7

- Mašláň, M., D. Žák : Logické obvody I., PřF UP Olomouc, 1993

- Doc. Ing. Jiří Bayer, CSc; Dr.Ing. Zdeněk Hanzálek; Ing. Richard Šusta: Logické systémy pro řízení, Vydavatelství ČVUT, Fakulta elektrotechnická, Praha, 2000, ISBN 80-01-02147-5

Související články

Externí odkazy

Obrázky, zvuky či videa k tématu klopný obvod na Wikimedia Commons

Obrázky, zvuky či videa k tématu klopný obvod na Wikimedia Commons  Obrázky, zvuky či videa k tématu Multivibrátory na Wikimedia Commons

Obrázky, zvuky či videa k tématu Multivibrátory na Wikimedia Commons  Obrázky, zvuky či videa k tématu Bistabilní KO na Wikimedia Commons

Obrázky, zvuky či videa k tématu Bistabilní KO na Wikimedia Commons

- Elektrické parametry logických obvodů, kombinační logické obvody, elektro.fs.cvut.cz

- Logické řízení, dce.felk.cvut.cz

- Logické systémy, dce.felk.cvut.cz

- Aplikace logických obvodů[nedostupný zdroj], dce.felk.cvut.cz

- Abíčko, Klopné obvody IX.: http://www.iabc.cz/…

- Elektronika, Sekvenční logické systémy: http://lucy.troja.mff.cuni.cz/~tichy/…

- Tranzistorové klopné obvody: http://maturitanazamku.kvalitne.cz/pdf/ELN5.pdf Archivováno 22. 6. 2019 na Wayback Machine

- Popis časovače 555: http://nehudek.wz.cz/… Archivováno 18. 10. 2010 na Wayback Machine

- Popis obvodů 555 a 556: http://pandatron.cz/…

- Příklady zapojení NE555: http://pandatron.cz/…